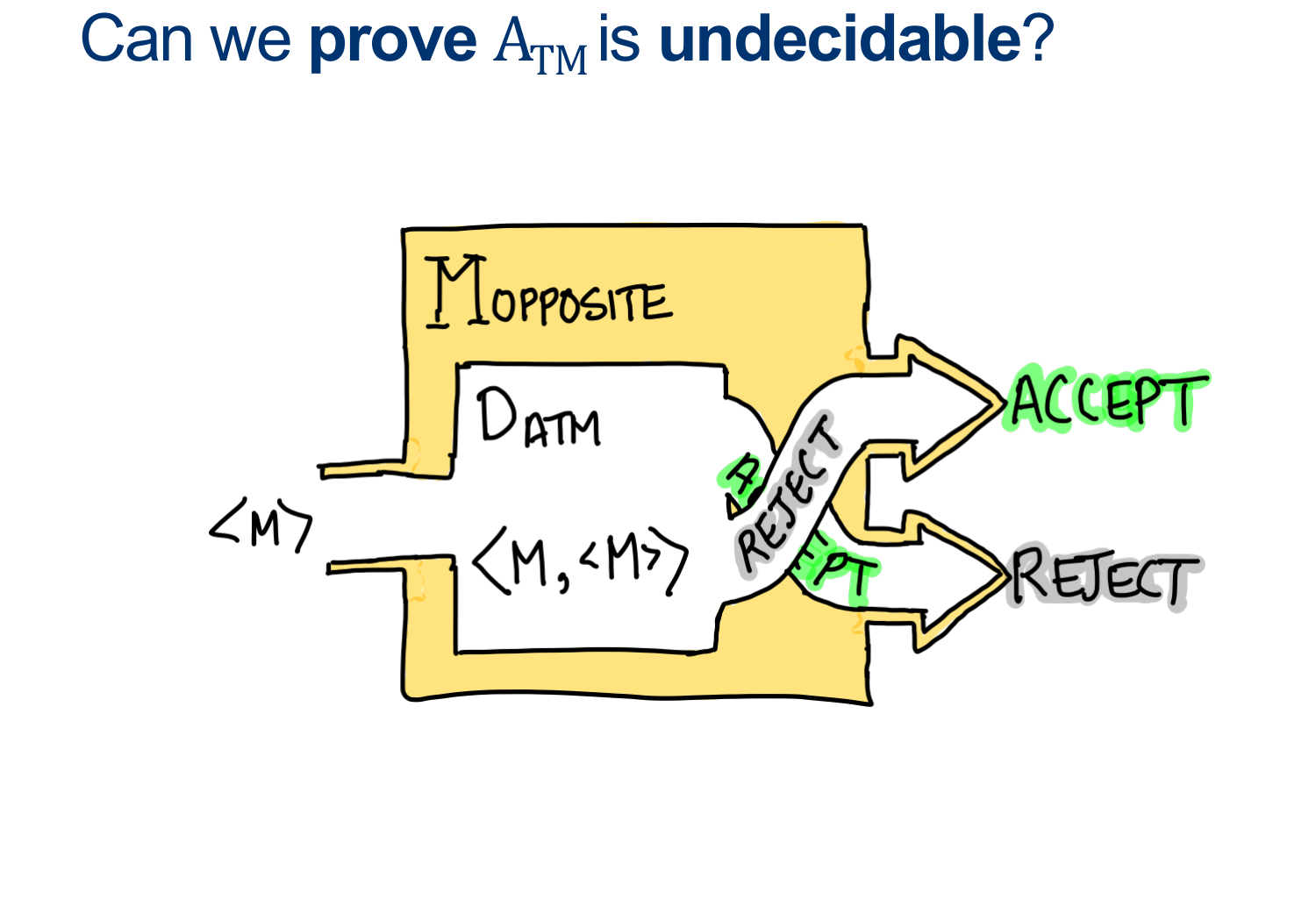

Think of a way you can get to say:

if we can solve HALT, we can, for sure, solve ATM

(Wait; then Click)

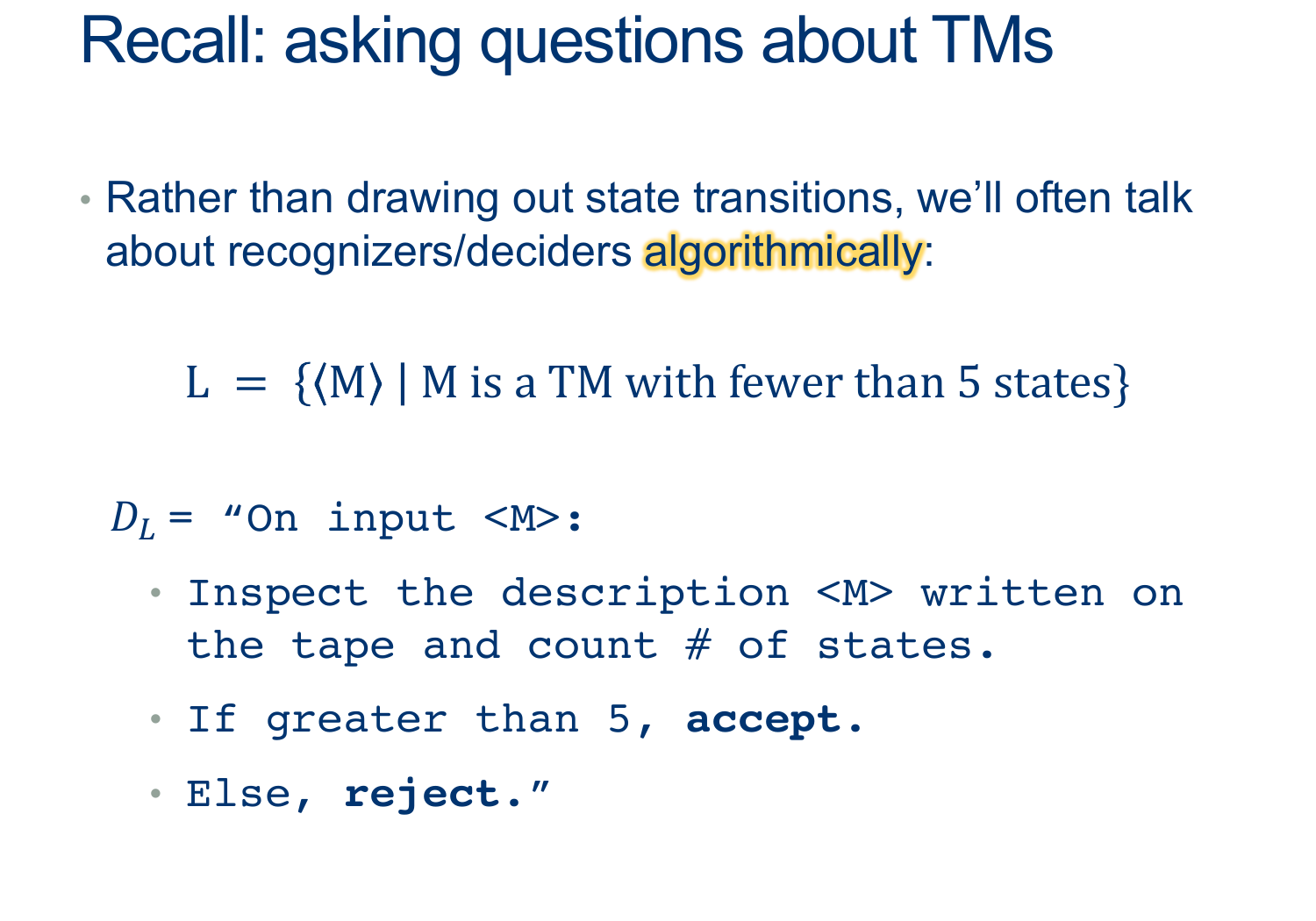

Assume HALT is decidable, and so there exists some \(D_{HALT}\) that decides, for any input \(< M,w>\), whether \(M\) halts on \(w\).

We'll design the Machine \(D_{ATM} \) as follows:

\[

\begin{align*}

&D_{ATM}:\\

& \text{ On input $ < M, w > $ }:\\

& \text{ Simulate $D_{HALT} \; on \; < M, w > $}\\

& \text{ If $D_{HALT}$ rejects, $M$ doesn't halt, so it did not accept: REJECT. }\\

& \text{ If $D_{HALT}$ accepts, we know $M$ won't loop forever, so }\\

& \quad \text{ Simulate $M$ on $w$ ADWID }\\

\end{align*}

\]

This machine is a decider for ATM (why?)

– it avoided the only problem we had with solving ATM, namely telling the difference between looping and lot waiting long enough.

However, we proved that ATM was undecidable by contradiction just a few minutes ago.

Aaaand...the only condition we need to build \(D_{ATM}\) was that \(D_{HALT}\) existed, so ...

\(D_{HALT} \; \) must not exist.